问题描述 字符移位:在8个7段管上显示HELLO_ _ _(可以显示下划线或不亮也可),每隔1秒钟,字符序列左移或右移一个七段管的位置。系统外部时钟50Mhz。左/右移位可以通过一个波动开关sw0来控制。

Verilog代码 主模块 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 module shift(clk50,sw0,reset,clk1,out0,out1,out2,out3,out4,out5,out6,out7); input clk50,sw0,reset; output wire clk1; output reg [6 :0 ] out0=7'b1110110 ; output reg [6 :0 ] out1=7'b1111001 ; output reg [6 :0 ] out2=7'b0111000 ; output reg [6 :0 ] out3=7'b0111000 ; output reg [6 :0 ] out4=7'b0111111 ; output reg [6 :0 ] out5=7'b0000000 ; output reg [6 :0 ] out6=7'b0000000 ; output reg [6 :0 ] out7=7'b0000000 ; divclk1hz t1(reset,clk50,clk1); always @(posedge clk1) begin if (sw0) begin out0<=out1; out1<=out2; out2<=out3; out3<=out4; out4<=out5; out5<=out6; out6<=out7; out7<=out0; end else begin out7<=out6; out6<=out5; out5<=out4; out4<=out3; out3<=out2; out2<=out1; out1<=out0; out0<=out7; end end endmodule

分频模块 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 module divclk1hz(reset,clk50,clk1); input clk50,reset;output reg clk1=0 ;integer i=1 ;always @(posedge clk50)begin if (!reset) begin i=1 ; end else begin if (i==25000000 ) begin i=1 ; clk1=~clk1; end else i=i+1 ; end end endmodule

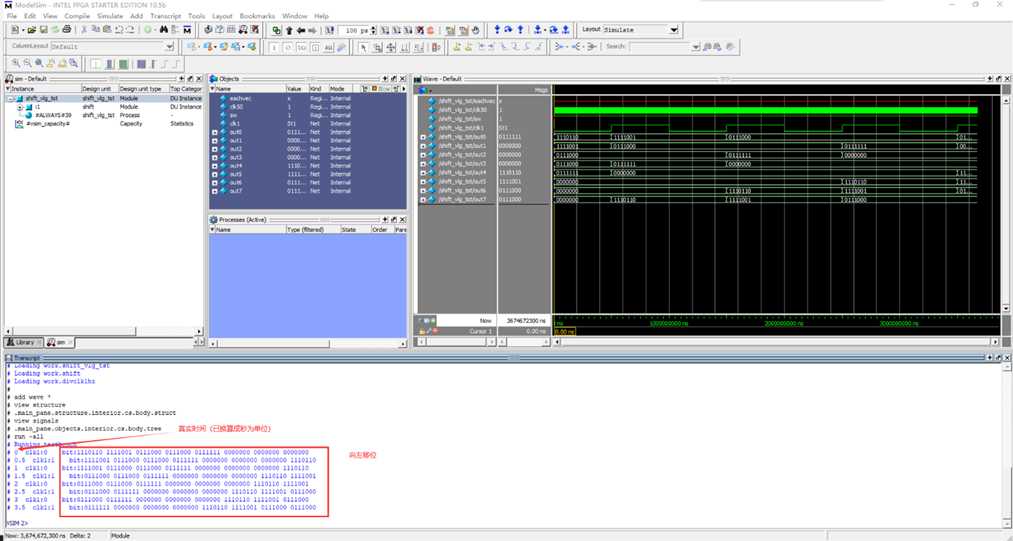

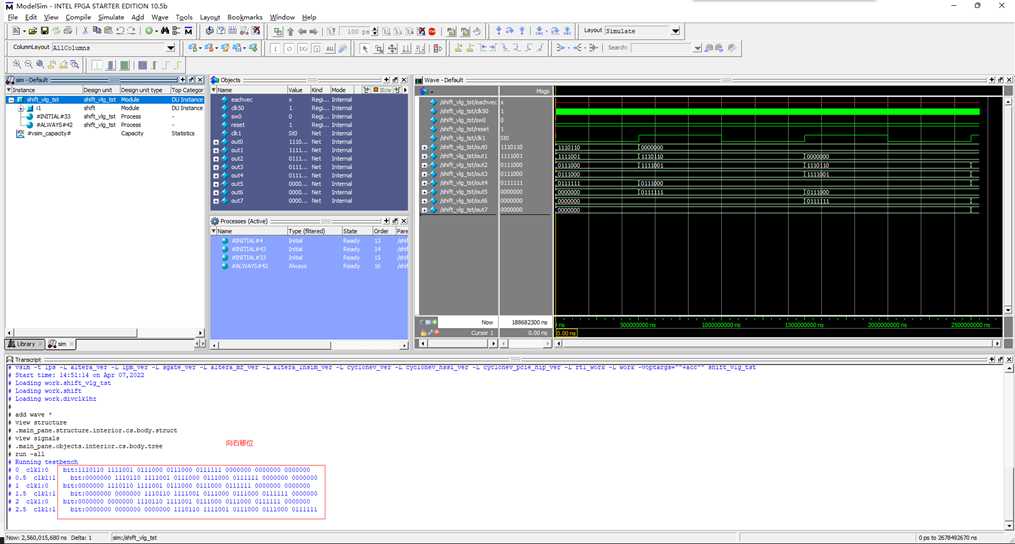

仿真测试代码 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 `timescale 1 ns/ 1 ns module shift_vlg_tst();reg eachvec;reg clk50;reg sw0;reg reset;wire clk1;wire [6 :0 ] out0;wire [6 :0 ] out1;wire [6 :0 ] out2;wire [6 :0 ] out3;wire [6 :0 ] out4;wire [6 :0 ] out5;wire [6 :0 ] out6;wire [6 :0 ] out7;shift i1 ( .clk1 (clk1), .clk50 (clk50), .out0 (out0), .out1 (out1), .out2 (out2), .out3 (out3), .out4 (out4), .out5 (out5), .out6 (out6), .out7 (out7), .sw0 (sw0), .reset (reset) ); initial begin $display ("Running testbench" ); clk50=1 ; sw0=1 ; reset=0 ; $monitor ($realtime /1000000000 ,,,"clk1:%d bit:%b %b %b %b %b %b %b %b" ,clk1,out0,out1,out2,out3,out4,out5,out6,out7); #20 reset=1 ; end always begin #10 clk50=~clk50; end endmodule

仿真测试结果 向左移位

向右移位

]

]