问题描述

将8个拨动开关作为8位并行输入,即对应数码为0000_0000—1111_1111,十进制数值为0-255,将编码对应的十进制数值显示在三个七段管上。比如若输入1000_0100对应十进制数为132,则在三个七段上显示1、3、2数字。建议七段管显示译码电路设计成模块,主模块采用模块调用的方式实现3个七段管的驱动。

verilog代码(task方式)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

| module bcdto7(bin,out1,out2,out3);

input [7:0] bin;

output reg[6:0] out1;

output reg[6:0] out2;

output reg[6:0] out3;

wire[3:0] bai;

wire[3:0] shi;

wire[3:0] ge;

assign ge=bin%10;

assign shi=(bin/10)%10;

assign bai=bin/100;

always@(bin)

begin

if(bin<10)

begin

show(ge,out1);

out2=7'b1111111;

out3=7'b1111111;

end

else if(bin<100)

begin

show(ge,out1);

show(shi,out2);

out3=7'b1111111;

end

else

begin

show(ge,out1);

show(shi,out2);

show(bai,out3);

end

end

task show;

input integer decc;

output reg[6:0] outt;

if(decc==0) outt=7'b1000000;

else if(decc==1) outt=7'b1111001;

else if(decc==2) outt=7'b0100100;

else if(decc==3) outt=7'b0110000;

else if(decc==4) outt=7'b0011001;

else if(decc==5) outt=7'b0010010;

else if(decc==6) outt=7'b0000010;

else if(decc==7) outt=7'b1111000;

else if(decc==8) outt=7'b0000000;

else if(decc==9) outt=7'b0011000;

else outt=7'b1111111;

endtask

endmodule

|

verilog代码(模块调用方式)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

| module bcdto7(bin,out1,out2,out3);

input [7:0] bin;

output [6:0] out1;

output [6:0] out2;

output [6:0] out3;

wire[3:0] bai;

wire[3:0] shi;

wire[3:0] ge;

assign ge=bin%10;

assign shi=(bin/10)%10;

assign bai=bin/100;

show t1(ge,out1);

show t2(shi,out2);

show t3(bai,out3);

endmodule

module show(

input [3:0]dec1,

output reg [6:0] u_out);

always@(dec1)

begin

case(dec1)

4'b0000:u_out=7'b1000000;

4'b0001:u_out=7'b1111001;

4'b0010:u_out=7'b0100100;

4'b0011:u_out=7'b0110000;

4'b0100:u_out=7'b0011001;

4'b0101:u_out=7'b0010010;

4'b0110:u_out=7'b0000010;

4'b0111:u_out=7'b1111000;

4'b1000:u_out=7'b0000000;

4'b1001:u_out=7'b0010000;

default:u_out = 7'b1111111;

endcase

end

endmodule

|

仿真测试代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

| `timescale 1 ps/ 1 ps

module bcdto7_vlg_tst();

reg [7:0] bin;

wire [6:0] out1;

wire [6:0] out2;

wire [6:0] out3;

integer i;

bcdto7 i1 (

.bin(bin),

.out1(out1),

.out2(out2),

.out3(out3)

);

initial

begin

for(i=0;i<256;i=i+1)

begin

bin[0]=(i/1)%2;

bin[1]=(i/2)%2;

bin[2]=(i/4)%2;

bin[3]=(i/8)%2;

bin[4]=(i/16)%2;

bin[5]=(i/32)%2;

bin[6]=(i/64)%2;

bin[7]=(i/128)%2;

#1;

end

$display("begin");

end

initial

$monitor($realtime,,,"dec:%d bit:%b %b %b",bin,out3,out2,out1);

endmodule

|

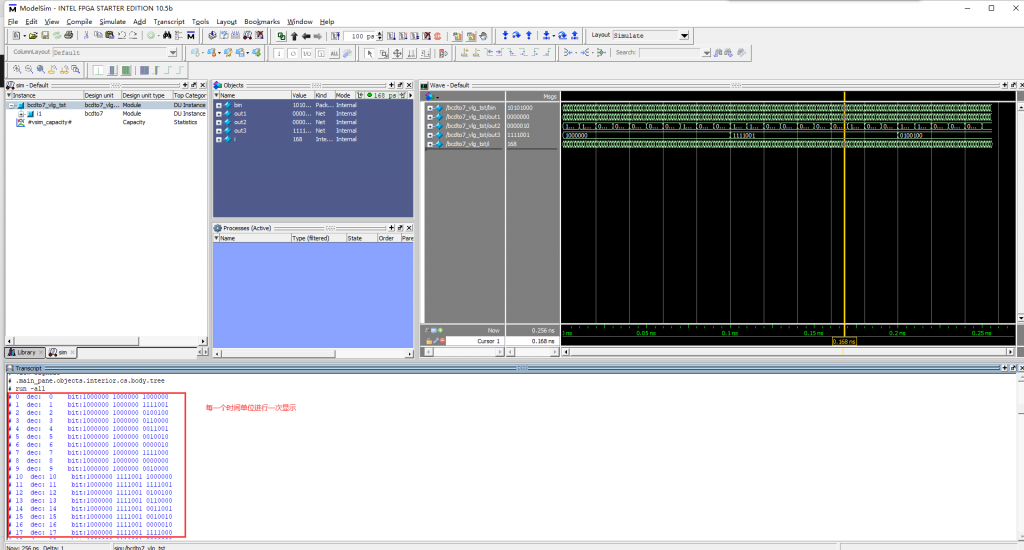

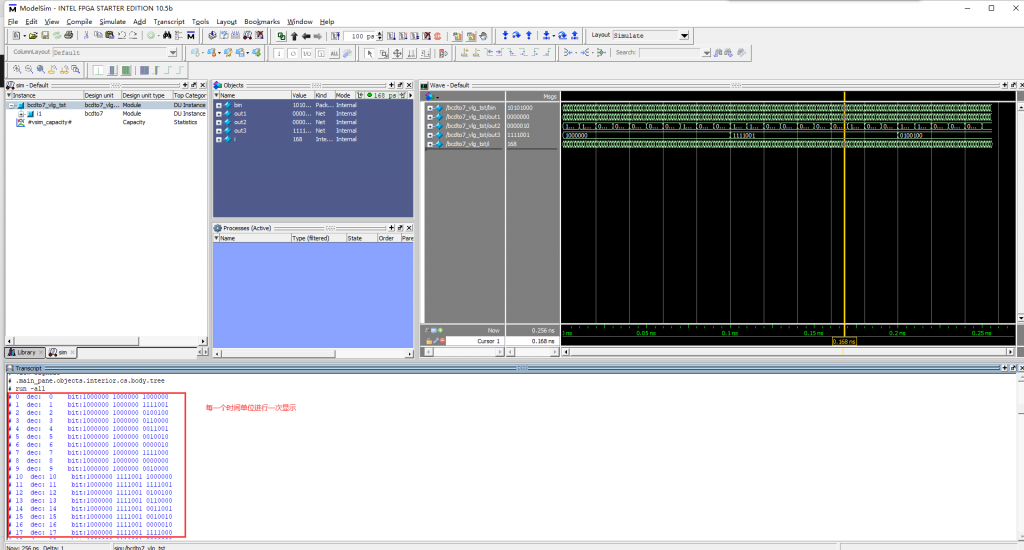

仿真结果