问题描述

74LS148是带有扩展功能的8-3线优先编码器,它有8个信号输入端,3个二进制码输出端(0-7),一个输入使能端(EI),一个选通输出端(EO)和一个扩展端(GS)。使能端为“0”时,该芯片被选中,否则不被选中。选通输出端和扩展端主要用于功能扩展。

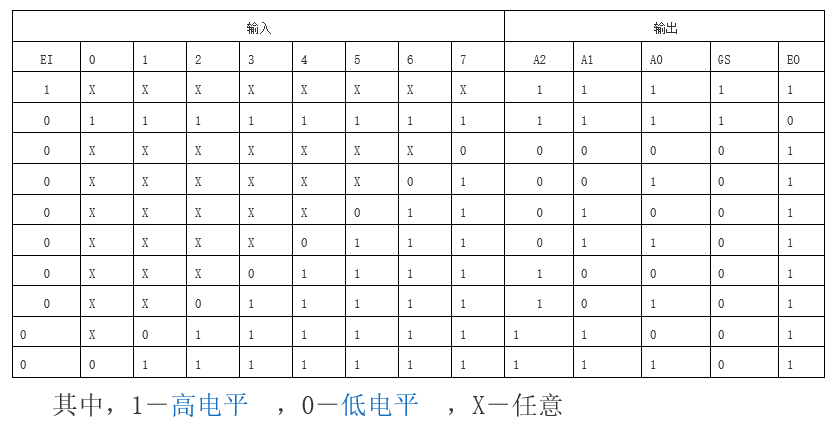

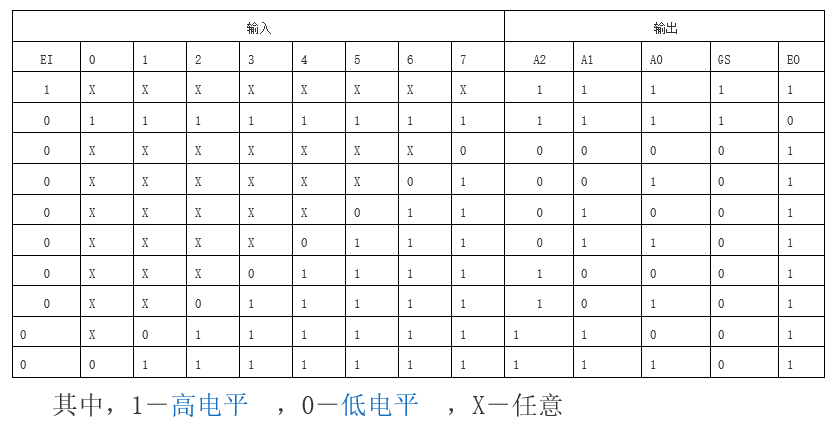

74LS148真值表

0-7 编码输入端(低电平有效)

A0、A1、A2 三位二进制编码输出信号即编码 输 出 端(低电平有效)

GS 片优先编码输出端即宽展端(低电平有效)

EO 选通输出端,即使能输出端

verilog代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

| module code83(in8,out3,EI,GS,EO);

input[7:0] in8;

input EI;

output reg[2:0] out3;

output reg GS;

output reg EO;

always@(in8,EI)

begin

out3=3'b111;

EO=1;

GS=1;

if(~EI)

begin

GS=0;

case(in8)

8'b11111111:

begin

EO=0;

GS=1;

out3=3'b111;

end

8'b00000000: out3=3'b000;

8'b10000000: out3=3'b001;

8'b11000000: out3=3'b010;

8'b11100000: out3=3'b011;

8'b11110000: out3=3'b100;

8'b11111000: out3=3'b101;

8'b11111100: out3=3'b110;

8'b11111110: out3=3'b111;

default: out3=3'b001;

endcase

end

end

endmodule

|

仿真测试代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

| `timescale 1 ps/ 1 ps

module code83_vlg_tst();

reg eachvec;

reg EI;

reg [7:0] in8;

wire EO;

wire GS;

wire [2:0] out3;

integer i;

code83 i1 (

.EI(EI),

.EO(EO),

.GS(GS),

.in8(in8),

.out3(out3)

);

initial

begin

$display("Running testbench");

EI=1;in8=8'b0;

#5;

EI=0;

in8=8'b11111111;

#1;

for(i=0;i<8;i=i+1)

begin

in8=in8<<1;

#1;

end

end

initial

$monitor($realtime,,,"EI:%b; input:%b; output:%b GS:%b; EO:%b",EI,in8,out3,GS,EO);

endmodule

|

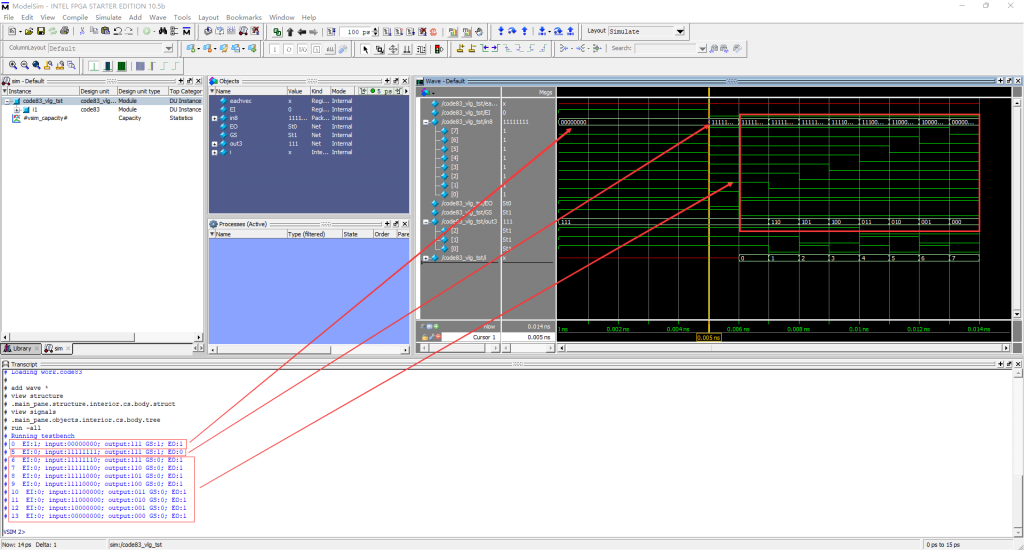

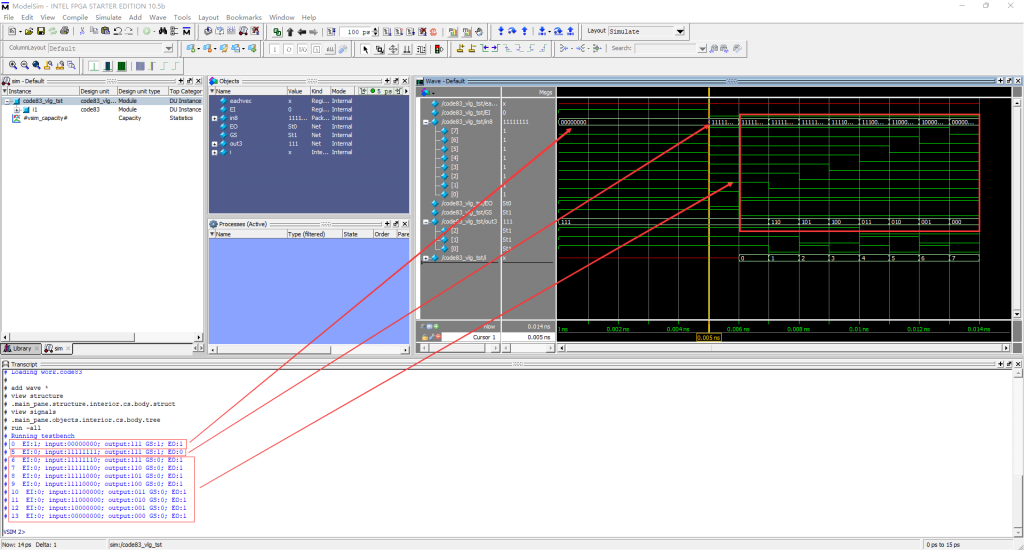

仿真结果