问题

时序电路设计并测试,设计一个模24的计数器。具有高电平的异步复位信号rst、同步置数信号load、上升沿触发时钟clk,置数数输入data,输出计数值sum和进位值cont。测试信号通过monitor或display文本显示。

verilog代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

| module count24(rst,load,clk,data,sum,cont);

input rst,load,clk;

input [4:0] data;

output sum;

output cont;

reg [4:0] sum;

initial

begin

sum=5'b00000;

end

always @(posedge clk or negedge rst)

begin

if(!rst) sum=5'b00000;

else if(load) sum=data;

else if(sum==5'b10111) sum=0;

else sum=sum+1'b1;

end

assign cont = sum[0]&sum[1]&sum[2]&sum[4];

endmodule

|

仿真测试代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

| `timescale 1ps/1ps

module count24_vlg_tst();

reg eachvec;

reg clk;

reg [4:0] data;

reg load;

reg rst;

wire cont;

wire [4:0] sum;

count24 i1 (

.clk(clk),

.cont(cont),

.data(data),

.load(load),

.rst(rst),

.sum(sum)

);

initial

begin

$display("Running testbench");

clk=0;

rst=1;

load=0;

data=5'b01010;

#5 rst=0;

#1 $display("rst:%b -- sum:%b", rst,sum);

rst=1;

#5 load=1;

#1 $display("load:%b -- sum:%b", load,sum);

load=0;

#100 $stop;

end

always

begin

#1 clk=~clk; $display("sum:%b -- cont:%b", sum,cont);

end

endmodule

|

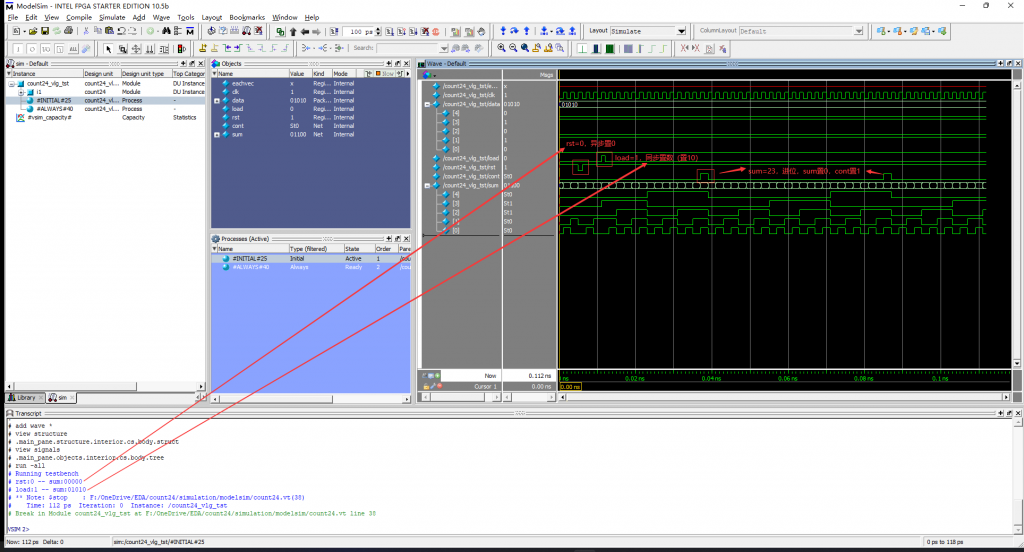

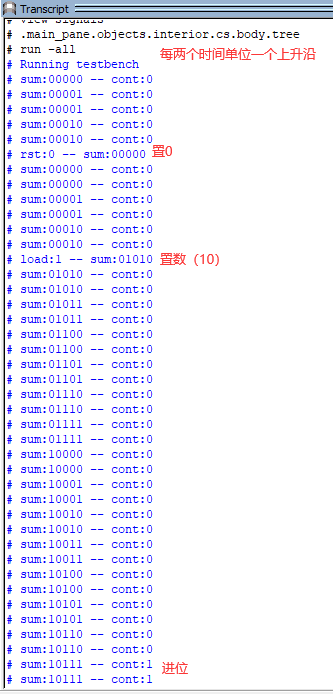

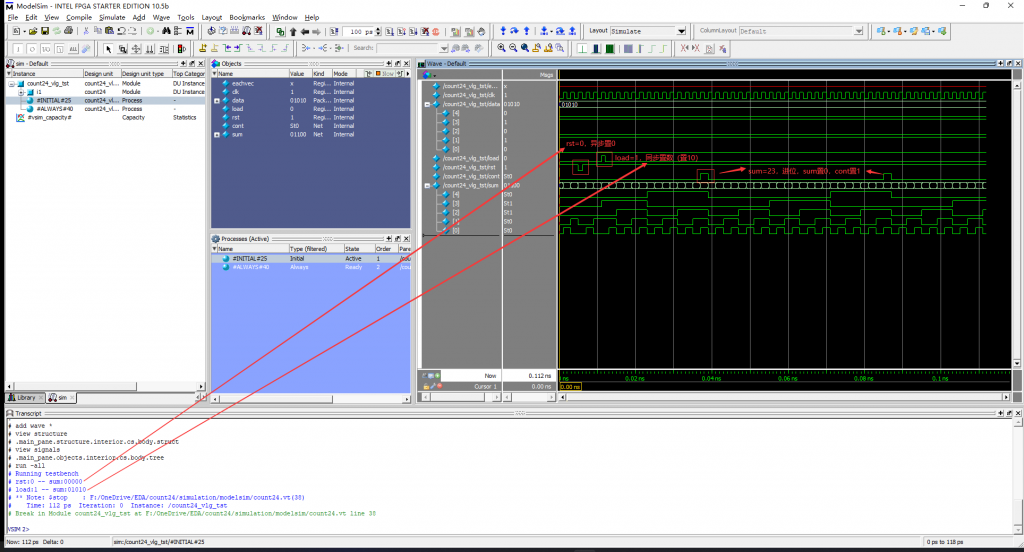

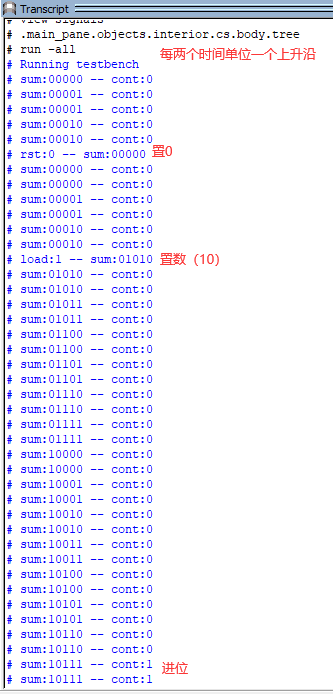

仿真结果