问题

组合电路设计并测试,设计一个实现10裁判电路设计,并设计测试文件进行测试,查看测试结果是否符合逻辑要求。每个裁判同意或不同意,裁判结果分为通过(同意人数多)、不通过(不同意人数多)、待定(同意与不同意相等)。

verilog代码

1

2

3

4

5

6

7

8

9

10

11

12

13

| module lab10(a,out);

input[9:0] a;

output out;

reg[1:0] out;

reg[3:0] sum;

always@(a,sum,out)

begin

sum=a[0]+a[1]+a[2]+a[3]+a[4]+a[5]+a[6]+a[7]+a[8]+a[9];

if(sum>5) out=2'b01;

else if(sum<5) out=2'b00;

else out=2'b10;

end

endmodule

|

仿真测试代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

| `timescale 1 ps/ 1 ps

module lab10_vlg_tst();

reg eachvec;

reg [9:0] a;

wire [1:0] out;

lab10 i1 (

.a(a),

.out(out)

);

initial

begin

$display("Running testbench");

a=10'b1111111110;

#1 $display("input:%b -- out:%b", a,out);

#5 a=10'b0000000001;

#1 $display("input:%b -- out:%b", a,out);

#5 a=10'b1111100000;

#1 $display("input:%b -- out:%b", a,out);

#5 ;

end

always

begin

@eachvec;

end

endmodule

|

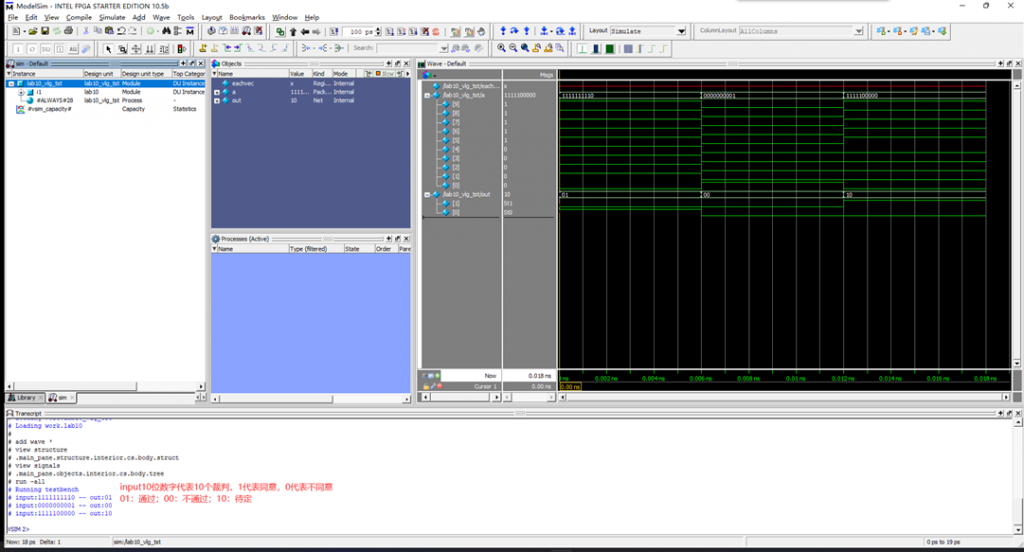

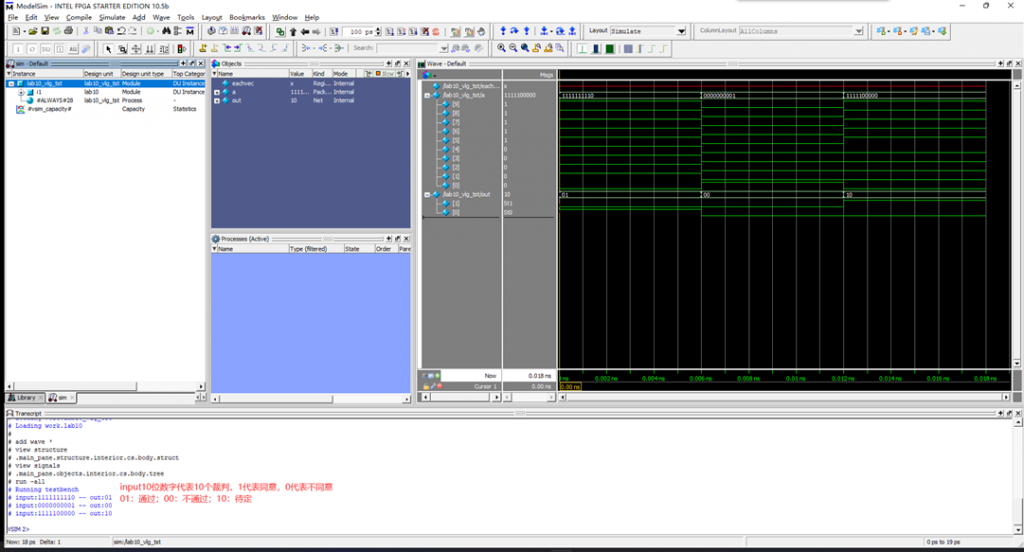

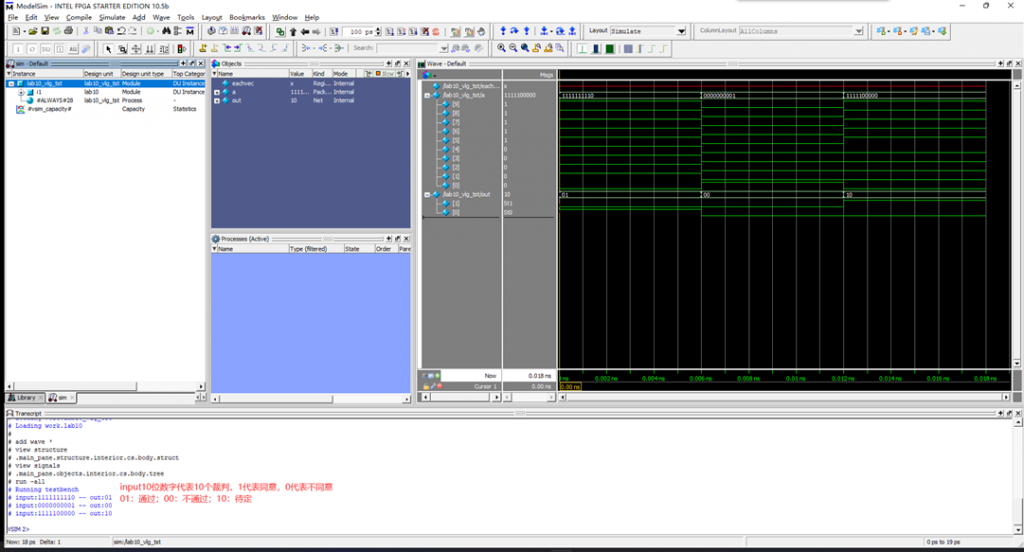

仿真结果